# Single Phase AC/DC Energy Measurement IC

#### 1. Product Features

Supports measurements of current/voltage RMS values, active power, reactive power, active energy, reactive energy, and other parameters.

- 1U2I mode supporting 2 current channels and 1 voltage channel measurement

- High accuracy:

- Nonlinear measurement error for active energy < 0.1% within input dynamic range (5000:1)

- Nonlinear error for voltage/current RMS values < 0.1% within measurement dynamic range (2500:1)

- Configurable filter for input waveforms to obtain full-wave, fundamental wave, or DC RMS values and power

- DC signal measurement capability:

- Input range: 2000:1

- Measurement error < ±1%

- Built-in waveform registers for waveform analysis

- Integrated registers for active/reactive energy, current/voltage RMS values

- SPI/UART communication interface

- Anti-creep design to ensure noise cut-off under zero-current conditions

- Power failure monitoring: Chip resets when VDD < 2.7V</li>

- Built-in reference voltage source

- Internal oscillator with ~4MHz clock frequency

- Single 3.3V supply with low power consumption: 15mW (typical)

# 2. Product Applications

- Circuit breakers

- Lighting energy consumption monitoring systems

- Energy meters

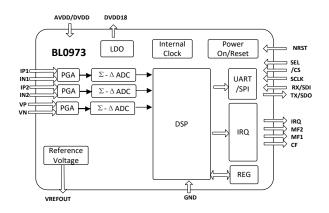

#### 3. Product Overview

BL0973 is a single-phase three-channel energy metering chip with an internal clock. It integrates three high-precision Sigma-Delta ADCs, enabling simultaneous measurement of two current channels and one voltage channel.

BL0973 allows users to select different filters for input waveforms to obtain full-wave, fundamental wave, or DC electrical parameters.

Functional Block Diagram

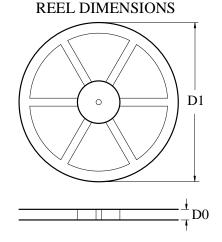

# 4. Ordering Guide

| Product Number | Package | Operating Temp. | Eco Status | MSL | Minimum Pack Qty |

|----------------|---------|-----------------|------------|-----|------------------|

| BL0973         | TSSOP28 | -40~85°C        | Green      | 3   | 3000             |

# **Contents**

| 1. | Product Features                                        | 1  |

|----|---------------------------------------------------------|----|

| 2. | Product Applications                                    | 1  |

| 3. | Product Overview                                        | 1  |

| 4. | Ordering Guide                                          | 1  |

| 5. | Package and Pin Function Description                    | 5  |

| 6. | Product Specifications                                  | 6  |

|    | 6.1 Electrical Parameter Specifications                 | 6  |

|    | 6.2 Absolute Maximum Ratings                            | 8  |

| 7. | Detailed Description                                    | 9  |

|    | 7.1 Operating Principle                                 | 9  |

|    | 7.1.1 Current and Voltage Waveform Generation Principle | 9  |

|    | 7.1.1.1 PGA Gain Adjustment                             | 9  |

|    | 7.1.1.2 Channel Offset Calibration                      | 9  |

|    | 7.1.1.3 Channel Gain Calibration                        | 10 |

|    | 7.1.1.4 Current/Voltage Waveform Output                 | 10 |

|    | 7.1.2 Active Power Calculation Principle                | 12 |

|    | 7.1.2.1 Selection of Active Waveform                    | 12 |

|    | 7.1.2.2 Active Power Output                             | 12 |

|    | 7.1.2.3 Active Power Calibration                        | 12 |

|    | 7.1.2.4 Phase Compensation                              | 13 |

|    | 7.1.2.5 Anti-Creep for Active Power                     | 14 |

|    | 7.1.2.6 Small-Signal Compensation for Active Power      | 14 |

|    | 7.1.3 Active Energy Measurement Principle               | 14 |

|    | 7.1.3.1 Active Energy Output                            | 15 |

|    | 7.1.3.2 Active Energy Output Selection                  | 15 |

|    | 7.1.3.3 Active Energy Output Scaling                    | 15 |

|    | 7.1.4 Current and Voltage RMS Calculation Principle     | 16 |

|    | 7.1.4.1 RMS Output                                      | 16 |

|    | 7.1.4.2 RMS Input Signal Configuration                  | 17 |

|    | 7.1.4.3 RMS Refresh Rate Setting                        | 17 |

|    | 7.1.4.4 Current/Voltage RMS Calibration                 | 17 |

|    | 7.1.4.5 RMS Anti-Creep Function                         | 18 |

|    | 7.1.5 Principle of Fast RMS Detection                   | 18 |

|    | 7.1.5.1 Fast RMS Output                                 | 19 |

|    | 7.1.5.2 Fast RMS Input Selection                        | 19 |

| 7.1.5.3 Fast RMS Accumulation Time and Threshold             | 19 |

|--------------------------------------------------------------|----|

| 7.1.5.4 Power Grid Frequency Selection                       | 20 |

| 7.1.5.5 Fast RMS Overlimit Data Storage                      | 20 |

| 7.1.5.6 Overcurrent Indication                               | 20 |

| 7.1.5.7 Relay Control                                        | 21 |

| 7.1.6 Electrical Parameter Measurement                       | 21 |

| 7.1.6.1 Line Frequency Measurement                           | 21 |

| 7.1.6.2 Phase Angle Calculation                              | 21 |

| 7.1.6.3 Power Sign Bit                                       | 22 |

| 7.1.7 Fault Detection                                        | 22 |

| 7.1.7.1 Zero-Crossing Detection                              | 22 |

| 7.1.7.2 Peak Overlimit                                       | 23 |

| 7.1.7.3 Line Voltage Sag                                     | 23 |

| 7.1.7.4 Zero-Crossing Timeout                                | 24 |

| 7.1.7.5 Power Supply Monitoring                              | 25 |

| 7.2. Internal Registers                                      | 25 |

| 7.2.1 Electrical Parameter Registers (Read-Only)             | 25 |

| 7.2.2 User Operation Registers                               | 28 |

| 7.2.3 Calibration Registers                                  | 29 |

| 7.2.4 Detailed Description of Electrical Parameter Registers | 34 |

| 7.2.4.1 Waveform Registers                                   | 34 |

| 7.2.4.2 RMS (Root Mean Square) Registers                     | 35 |

| 7.2.4.3 Active Power Registers                               | 35 |

| 7.2.4.4 Reactive Power Registers                             | 36 |

| 7.2.4.5 DC Power Registers                                   | 36 |

| 7.2.4.6 Apparent Power Registers                             | 36 |

| 7.2.4.7 Power Factor Registers                               | 36 |

| 7.2.4.8 Energy Registers                                     | 37 |

| 7.2.4.9 Energy Pulse Count Registers                         | 37 |

| 7.2.4.10 Power Sign Bit Register                             | 38 |

| 7.2.4.11 Peak Registers                                      | 38 |

| 7.2.4.12 Line Voltage Frequency Register                     | 38 |

| 7.2.4.13 Voltage-Current Phase Angle Registers               | 39 |

| 7.2.4.14 Status Registers                                    | 39 |

| 7.2.5 Detailed Description of User Operation Registers       | 39 |

| 7.2.5.1 User Write Protection Setting Register               | 39 |

| 7.2.5.2 Soft Reset Register                                  | 39 |

|     | 7.2.5.3 Output Mode Register                   | 40 |

|-----|------------------------------------------------|----|

|     | 7.2.5.4 User Mode Selection Register           | 41 |

|     | 7.2.5.5 Interrupt Mask Register                | 42 |

|     | 7.2.5.6 Read-with-Reset Configuration Register | 43 |

|     | 7.2.5.7 ADC Enable Control                     | 43 |

|     | 7.2.6 Calibration Register Details             | 44 |

|     | 7.2.6.1 PGA Channel Gain Adjustment            | 44 |

|     | 7.2.6.2 Phase Correction Related Registers     | 44 |

|     | 7.2.6.3 Channel Offset Adjustment              | 45 |

|     | 7.2.6.4 Channel Gain Adjustment                | 47 |

|     | 7.2.6.5 RMS Offset Calibration                 | 47 |

|     | 7.2.6.6 RMS Gain Adjustment                    | 48 |

|     | 7.2.6.7 Power Offset Calibration               | 48 |

|     | 7.2.6.8 Power Gain Adjustment                  | 49 |

|     | 7.2.6.9 Anti-Creep Threshold Settings          | 50 |

|     | 7.2.6.10 CF Scaling Factor Configuration       | 50 |

|     | 7.2.7 Fault Detection Configuration            | 51 |

| 8.  | Application Information                        | 51 |

|     | 8.1 Communication Interface                    | 51 |

|     | 8.1.1 SPI                                      | 51 |

|     | 8.1.1.1 Overview                               | 51 |

|     | 8.1.1.2 Operating Mode                         | 51 |

|     | 8.1.1.3 Frame Structure                        | 52 |

|     | 8.1.1.4 Read Operation Timing                  | 53 |

|     | 8.1.1.5 Write Operation Timing                 | 53 |

|     | 8.1.2 UART                                     | 54 |

|     | 8.1.2.1 Overview                               | 54 |

|     | 8.1.2.2 Byte Format                            | 54 |

|     | 8.1.2.3 Read Timing                            | 54 |

|     | 8.1.2.4 Write Timing                           | 55 |

|     | 8.1.2.5 UART Interface Protection Mechanism    | 56 |

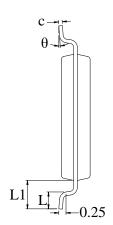

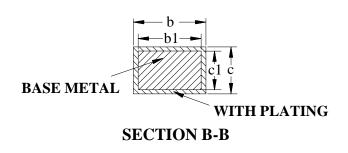

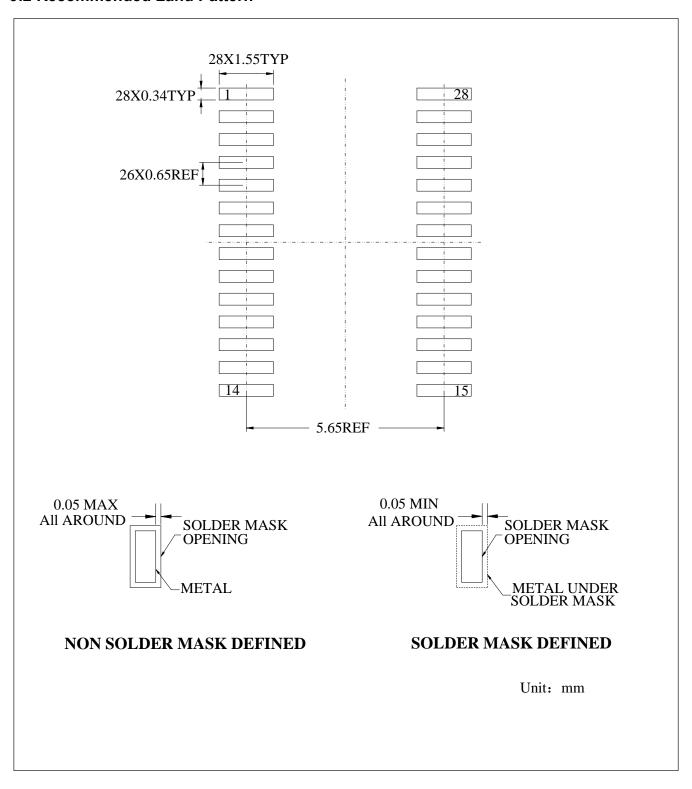

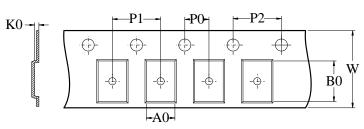

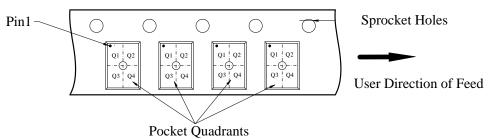

| 9.  | Package Information                            | 57 |

|     | 9.1 Outline Dimensions                         | 57 |

|     | 9.2 Recommended Land Pattern                   | 58 |

|     | 9.3 Marking                                    | 59 |

| 10. | Packing Specifications                         | 60 |

| Re  | vision History                                 | 61 |

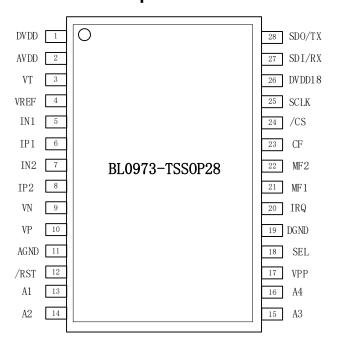

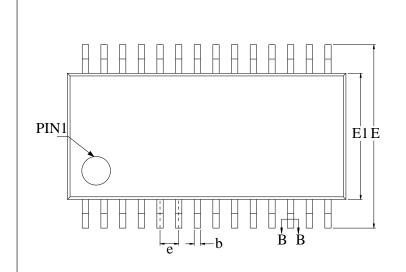

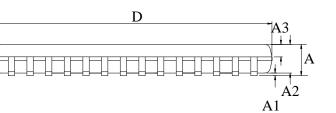

# 5. Package and Pin Function Description

Figure 1 TSSOP28 Pins

Table 1 TSSOP28 Pin Configuration

| Pin No | Function | I/O | Description                                                                                                         |

|--------|----------|-----|---------------------------------------------------------------------------------------------------------------------|

| 1      | DVDD     | 1   | Digital power supply input (3.3V)                                                                                   |

| 2      | AVDD     | 1   | Analog power supply input (3.3V)                                                                                    |

| 3      | VT       | 1   | NC                                                                                                                  |

| 4      | VREF     | I/O | Reference voltage input/output, connect external 0.1µF filter capacitor                                             |

| 5,6    | IN1, IP1 | I   | Current channel A signal input with adjustable gain (x8~x32). Maximum differential voltage per pin pair: ±175mV pp. |

| 7,8    | IN2, IP2 | I   | Current channel B signal input with adjustable gain (x8~x32). Maximum differential voltage per pin pair: ±175mV pp. |

| 9,10   | VN, VP   | I   | Voltage channel signal input with adjustable gain (x8~x32). Maximum differential voltage per pin pair: ±175mV pp.   |

| 11     | AGND     | 1   | Ground reference for the analog circuitry.                                                                          |

| 12     | /RST     | 1   | Reset pin (active low)                                                                                              |

| 13     | A1       |     |                                                                                                                     |

| 14     | A2       | 1.  | Chin address setting for LIADT interfess                                                                            |

| 15     | A3       | 1   | Chip address setting for UART interface                                                                             |

| 16     | A4       | 1   |                                                                                                                     |

| 17     | VPP      | I   | NC                                                                                                                  |

| 18     | SEL      | 1   | Communication mode selection (SPI/UART)                                                                             |

| 19     | DGND     | I   | Ground reference for the digital curcuitry                                                                          |

| 20 | /IRQ   | 0   | Interrupt output                                                       |

|----|--------|-----|------------------------------------------------------------------------|

| 21 | MF1    | 0   | Logic output                                                           |

| 22 | MF2    | 0   | Logic output                                                           |

| 23 | CF     | 0   | Energy calibration pulse output                                        |

| 24 | /CS    | I   | SPI chip select / UART mode baud rate selection                        |

| 25 | SCLK   | I   | SPI communication clock / UART mode baud rate selection                |

| 26 | DVDD18 | I/O | Digital 1.8V input/output pin, connect external 0.1µF filter capacitor |

| 27 | SDI/RX | I   | SPI/UART communication pin (data receive)                              |

| 28 | SDO/TX | 0   | SPI/UART communication pin (data transmit)                             |

|    | •      |     |                                                                        |

# 6. Product Specifications

# **6.1 Electrical Parameter Specifications**

Table 2 Electrical Parameters

(VDD=3.3V, GND=0V, on-chip voltage reference, built-in crystal oscillator, 25°C, energy measured via the CF output.)

| Parameter                                             | Symbol               | Test Condition                              | Min | Тур  | Max | Unit |

|-------------------------------------------------------|----------------------|---------------------------------------------|-----|------|-----|------|

| Active Power Measurement Error                        | WATT <sub>ERR</sub>  | 5000: 1 input DR                            |     | 0.1  |     | %    |

| Measurement Error Caused by Inter-Channel Phase Angle |                      |                                             |     |      |     |      |

| (PF=0.8 Capacitive)                                   | PF08C <sub>ERR</sub> | Phase Lead 37°                              |     | 0.1  |     | %    |

| (PF=0.5 Inductive)                                    | PF05Lerr             | Phase Lag 60°                               |     | 0.1  |     | %    |

| AC Power Supply Rejection                             | ACpsrr               | Current Channel Input<br>Pins IP\IN @100mV, |     | 0.01 |     | %    |

| (Output Frequency<br>Amplitude Variation)             |                      |                                             |     |      |     |      |

| DC Power Supply<br>Rejection                          | DC <sub>PSRR</sub>   | Voltage Channel Input Pins VP\VN=100mV      |     | 0.1  |     | %    |

| (Output Frequency<br>Amplitude Variation)             |                      |                                             |     |      |     |      |

| Voltage RMS Measurement Accuracy, Relative Error      | VRMS <sub>ERR</sub>  | 2500: 1 input DR                            |     | 0.1  |     | %    |

# **BL0973**

| Current RMS Measurement Accuracy, Relative Error | IRMS <sub>ERR</sub> | 2500: 1 input DR                   |      | 0.1    |      | %      |

|--------------------------------------------------|---------------------|------------------------------------|------|--------|------|--------|

| Analog Input                                     |                     |                                    |      |        |      |        |

| Input Level (Peak)                               |                     | Differential Input                 |      |        | 175  | mV     |

| Input Impedance                                  |                     |                                    |      | 37     |      | kΩ     |

| Bandwidth (-3dB)                                 |                     |                                    |      | 14     |      | kHz    |

| Gain Error                                       |                     | External 1.2V Reference Voltage    |      | 0.5    |      | %      |

| Inter-Phase Gain<br>Matching Error               |                     | External 1.2V Reference<br>Voltage |      | 0.3    |      | %      |

| Internal Voltage Reference                       | Vref                |                                    |      | 1.0975 |      | V      |

| Reference Deviation                              | Vref <sub>ERR</sub> |                                    |      | 5      |      | mV     |

| Temperature Coefficient                          | TempCoef            |                                    |      | 20     |      | ppm/°C |

| Logic Input                                      |                     |                                    |      |        |      |        |

| SDI, SCLK, /CS                                   |                     |                                    |      |        |      |        |

| Input High Level                                 |                     | VDD=3.3V±2.5%                      | 2.6  |        |      | V      |

| Input Low Level                                  |                     | VDD=3.3V±2.5%                      |      |        | 0.8  | V      |

| Logic Output                                     |                     |                                    |      |        |      |        |

| SDO, DO1, DO2, CF,                               |                     |                                    |      |        |      |        |

| Output High Level                                |                     | VDD=3.3V±2.5%                      | 2.6  |        |      | V      |

| Output Low Level                                 |                     | VDD=3.3V±2.5%                      |      |        | 1    | V      |

| Power Supply                                     |                     |                                    |      |        |      |        |

| VDD                                              | V <sub>VDD</sub>    |                                    | 3    | 3.3    | 3.6  | V      |

| DVDD18                                           | V <sub>DVDD18</sub> | VDD18=1.8V                         | 1.62 | 1.8    | 1.98 | V      |

| IDD                                              | I <sub>VDD</sub>    | VDD=3.3                            |      | 4      | 6    | mA     |

# **6.2 Absolute Maximum Ratings**

Table 3 Absolute Maximum Ratings (T = 25°C)

| Item                                      | Symbol                   | Limit          | Unit |

|-------------------------------------------|--------------------------|----------------|------|

| Supply Voltage VDD                        | VDD                      | -0.3 ~ +4      | V    |

| Supply Voltage DVDD18                     | DVDD18                   | -0.3 ~ +2.5    | V    |

| Analog Input Voltage (relative to AGND)   | IN1、IP1、IN2、IP2、VP、VN、VT | -1 ~ +VDD      | V    |

| Analog Output Voltage (relative to AGND)  | Vref                     | -0.3 ~ +VDD    | V    |

| Digital Input Voltage (relative to DGND)  | /SDI、SCLK、/CS            | -0.3 ~ VDD+0.3 | V    |

| Digital Output Voltage (relative to DGND) | CF、MF1、MF2、SDO、/IRQ      | -0.3 ~ VDD+0.3 | V    |

| Operating Temperature                     | Topr                     | -40 ~ +85      | °C   |

| Storage Temperature                       | Tstr                     | -55 ~ +150     | °C   |

# 7. Detailed Description

## 7.1 Operating Principle

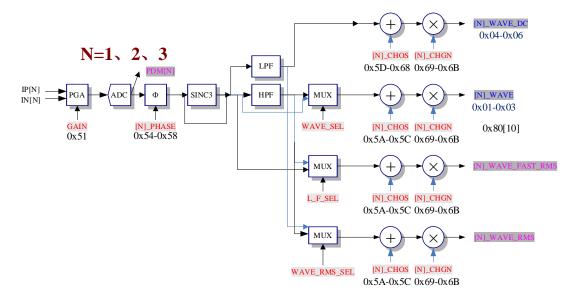

#### 7.1.1 Current and Voltage Waveform Generation Principle

Figure 2 Waveform Generation Signal Chain

As shown in the figure above, three identical high-precision ADCs with differential input structures are employed: the current channel and voltage channel respectively receive positive/negative voltage signals IP1, IN1, IP2, IN2, and VP, VN.

Within each channel, the input signals pass through a programmable gain amplifier (PGA) in the analog module and a high-precision analog-to-digital converter (ADC). The converted PDM codes are then transmitted to the digital module.

The digital module processes the data through phase calibration, a decimation filter (SINC3), an optional high-pass filter (HPF) or DC-blocking low-pass filter (LPF), followed by gain and offset correction modules. This yields the required current waveform data (IA\_WAVE, IB\_WAVE) and voltage waveform data (V WAVE).

#### 7.1.1.1 PGA Gain Adjustment

The PGA gains of both current and voltage channels are adjustable. The data format of the PGA gain adjustment register (GAIN) is as follows: (Each 4-bit field controls one channel: 0010 = 8; 0011 = 16; 0110 = 24; 0111 = 32).

AddrNameWidthDefault ValueDescription51GAIN120x000PGA Channel Gain Adjustment Register:<br/>[3:0]: Voltage channel; [7:4]: Current B channel; [11:8]: Current A channel

Table 4 PGA Gain Adjustment Register

### 7.1.1.2 Channel Offset Calibration

Includes three 16-bit channel offset calibration registers CHOS as follows, with a default value of 0x0000.

These registers use two's complement format data to eliminate the deviations introduced by analog-to-

digital conversion in current and voltage channels respectively. The deviations may originate from input signals or the inherent offset of the ADC circuit itself. Offset calibration ensures zero waveform offset under no-load conditions.

Table 5 Channel Offset Adjustment Register

| Addr | Name    | Bit Width | Default Value | Description                                                    |

|------|---------|-----------|---------------|----------------------------------------------------------------|

| 5A   | IA_CHOS | 16        | 0x0000        | Current Channel A Offset Adjustment Register, two's complement |

| 5B   | IB_CHOS | 16        | 0x0000        | Current Channel B Offset Adjustment Register, two's complement |

| 5C   | V_CHOS  | 16        | 0x0000        | Voltage Channel Offset Adjustment Register, two's complement   |

Bias Adjustment Calibration Formula:

where WAVE0 is the measured value of the channel, and WAVE is the calibrated output value.

#### 7.1.1.3 Channel Gain Calibration

Includes three 16-bit channel gain calibration registers CHGN as follows, with a default value of 0x0000.

Table 6 Channel Gain Adjustment Register

| Addr | Name    | Bit Width | Default Value | Description                                                  |

|------|---------|-----------|---------------|--------------------------------------------------------------|

| 69   | IA_CHGN | 16        | 0x0000        | Current Channel A Gain Adjustment Register, two's complement |

| 6A   | IB_CHGN | 16        | 0x0000        | Current Channel B Gain Adjustment Register, two's complement |

| 6B   | V_CHGN  | 16        | 0x0000        | Voltage Channel Gain Adjustment Register, two's complement   |

These registers use two's complement format data to compensate for gain errors introduced by the current and voltage channel analog-to-digital conversions. Such errors may originate from input sources or the ADC circuitry itself. The gain calibration allows adjustments within a range of ±50%.

Channel Gain Calibration Formula:

$$WAVE = WAVE0 * (1 + \frac{CHGN}{2^{16}})$$

where WAVE0 is the measured value of the channel and WAVE is the calibrated output value.

#### 7.1.1.4 Current/Voltage Waveform Output

Capable of acquiring real-time load current and voltage waveform data. The sampled current and voltage values are updated at approximately 15ksps, with 300 points sampled per waveform cycle. Each sampled data point is a 24-bit signed value stored in dedicated waveform registers (IA\_WAVE, IB\_WAVE, V\_WAVE).

Table 7 Waveform Registers

| Addr | Name       | Bit Width | Default Value | Description                         |

|------|------------|-----------|---------------|-------------------------------------|

| 1    | IA_WAVE    | 24        | 0x000000      | Current Channel A Waveform Register |

| 2    | IB_WAVE    | 24        | 0x000000      | Current Channel B Waveform Register |

| 3    | V_WAVE     | 24        | 0x000000      | Voltage Channel Waveform Register   |

| 4    | IA_WAVE_DC | 24        | 0x000000      | Current A DC Waveform Register      |

| 5    | IB_WAVE_DC | 24        | 0x000000      | Current B DC Waveform Register      |

| 6    | V_WAVE_DC  | 24        | 0x000000      | Voltage DC Waveform Register        |

The current waveform output selection can be configured through the user mode register MODE[10]. The voltage waveform output is the normal waveform (the waveform used for RMS calculation).

Table 8 Current Waveform Selection

| 0x44 | MODE1                  | Operation Mode Register   |                                                         |  |

|------|------------------------|---------------------------|---------------------------------------------------------|--|

| No.  | name                   | default value description |                                                         |  |

|      |                        |                           | Current waveform register output selection:             |  |

| [10] | [10] WAVE_REG_SEL 1'b0 |                           | Default 0 selects waveform from normal current channel. |  |

|      |                        |                           | 1 selects waveform output from fast measurement channel |  |

The normal waveform (for RMS calculation) is categorized into AC, DC, and full-wave modes. When using HPF, it operates in AC measurement mode and outputs the AC waveform. When using LPF (Low-Pass Filter) for DC measurement mode, it outputs the DC waveform. After SINC filtering, the full-wave waveform is obtained, which can be configured via the user mode register MODE.

Table 9 RMS waveform selection

| 0x44  | MODE         | Operation Mode Register   |                                                                                                                                   |  |

|-------|--------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| No.   | name         | default value description |                                                                                                                                   |  |

| [9:4] | WAVE_RMS_SEL | 2'b00                     | RMS waveform selection: 00-HPF, 10-DC, 01-SINC, 11-HPF [9:8]: Voltage channel; [7:6]: Current B channel; [5:4]: Current A channel |  |

The waveform of the fast measurement channel (used for fast RMS calculation) is divided into full-wave and AC full-wave modes. Full-wave waveform is output without passing through the HPF (High Pass Filter). AC measurement mode outputs AC full-wave waveform when passing through the HPF. This can be configured via the user mode register MODE[0].

Table 10 Fast measurement selection

| 0x44 | MODE1        | Operation Mode Register             |                                       |  |

|------|--------------|-------------------------------------|---------------------------------------|--|

| No.  | name         | default value                       | description                           |  |

| [0]  | I F OFI 1150 | Fast measurement selection via HPF, |                                       |  |

| [0]  | 0]           |                                     | 0-full wave (default), 1-AC full wave |  |

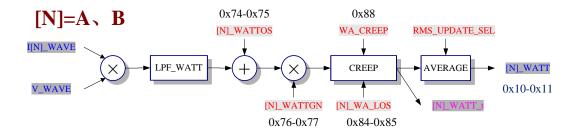

#### 7.1.2 Active Power Calculation Principle

Figure 3 Active Power Signal Chain

The power signal is obtained by digitally multiplying current and voltage waveforms, followed by sequential processing through a low-pass filter, gain and offset calibration, anti-creep judgment, and averaging.

#### 7.1.2.1 Selection of Active Waveform

The waveforms used for power calculation can be configured via the user mode register MODE.

Note: When calculating DC power, both current and voltage waveforms must be selected as DC for power computation.

Table 11 Active Power waveform selection

| 0x44  | MODE     | Operation Mode Register   |                                             |  |

|-------|----------|---------------------------|---------------------------------------------|--|

| No.   | name     | default value description |                                             |  |

| [3:1] | WAVE_SEL | 1'b0                      | Active power waveform selection: 0-AC, 1-DC |  |

#### 7.1.2.2 Active Power Output

The active power register is a 24-bit signed number in two's complement format. Bit[23] is the sign bit, indicating positive/negative power.

Table 12 Active Power Registers

| Addr | Name   | Bit Width | Default Value | Description                                     |

|------|--------|-----------|---------------|-------------------------------------------------|

| 10   | A_WATT | 24        | 0x000000      | Channel A active power, two's complement format |

| 11   | B_WATT | 24        | 0x000000      | Channel B active power, two's complement format |

#### 7.1.2.3 Active Power Calibration

There are two 16-bit active power offset correction registers (WATTOS) and two 16-bit active power gain correction registers (WATTGN), with default values of 0x0000.

WATTOS is used to eliminate DC offset in active power calculations, while WATTGN compensates for gain deviation in active power calculations. These deviations may originate from crosstalk between channels on the PCB or within the integrated circuit itself, or from inherent ADC channel gain mismatch.

Offset correction ensures that the active power register value approaches zero under no-load conditions.

Table 13 Active Power Adjustment Registers

| Addr | Name     | Bit Width | Default Value | Description                                                  |

|------|----------|-----------|---------------|--------------------------------------------------------------|

| 76   | A_WATTGN | 16        | 0x0000        | Active power gain adjustment for Channel A, two's complement |

| 77 | B_WATTGN | 16 | 0x0000 | Active power gain adjustment for Channel B, two's complement   |

|----|----------|----|--------|----------------------------------------------------------------|

| 74 | A_WATTOS | 16 | 0x0000 | Active power offset adjustment for Channel A, two's complement |

| 75 | B_WATTOS | 16 | 0x0000 | Active power offset adjustment for Channel B, two's complement |

Correction result of active power:

$$WATT = WATT0 * (1 + \frac{WATTGN}{2^{16}})$$

where WATT is the corrected active power, and WATT0 is the active power before correction.

# 7.1.2.4 Phase Compensation

The ADC output stage incorporates a digital calibration method for minor phase errors. It introduces a small time delay or advance into the signal processing circuit to compensate for slight phase deviations. Since this compensation must occur in-time, it is only applicable for minor phase errors within <0.6°. Using time-shift techniques to correct large phase errors would introduce significant phase distortions in higher-order harmonics.

The phase compensation for current and voltage channels is adjustable. The data format of the phase calibration register PHASE is as follows (each 8 bits calibrate one channel: [7] is reserved, [6:0] has a minimum adjustment delay of 250ns, corresponding to 0.0045 degrees/1LSB, with a maximum adjustable range of ±0.5715 degrees).

Table 14 phase calibration registers

| Addr | Name      | Bit<br>Width | Default<br>Value | Description                                                                                                                                                                                           |

|------|-----------|--------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52   | IRMS_P1   | 16           | 0x0100           | Phase angle segmentation point P1 definition, satisfying IRMSmin < P1 < P2 < IRMSmax                                                                                                                  |

| 53   | IRMS_P2   | 16           | 0x2000           | Phase angle segmentation point P2 definition, satisfying IRMSmin < P1 < P2 < IRMSmax                                                                                                                  |

| 54   | IA_PHCAL1 | 16           | 0x0000           | Current channel A phase calibration register 1. When IRMSmin < input current RMS < P1, [6:0] corrects current channel phase. When P1 < input current RMS < P2, [14:8] corrects current channel phase. |

| 55   | IA_PHCAL2 | 8            | 0x00             | Current channel A phase calibration register 2. When P2 < input current RMS < IRMSmax, [6:0] corrects current channel phase.                                                                          |

| 56   | IB_PHCAL1 | 16           | 0x0000           | Current channel B phase calibration register (same as address 54)                                                                                                                                     |

| 57   | IB_PHCAL2 | 8            | 0x00             | Current channel B phase calibration register (same as address 55)                                                                                                                                     |

| 58   | V_PHCAL   | 8            | 0x00             | Voltage channel phase calibration register (same as address 53)                                                                                                                                       |

# 7.1.2.5 Anti-Creep for Active Power

The chip integrates a patented anti-creep power module to ensure zero power output when no current is input.

The active anti-creep threshold register (WA\_CREEP) is a 12-bit unsigned value with a default setting of 0x04C. This value is multiplied by 2 and then compared with the absolute value of the input active power signal. If the absolute value of the input active power signal is smaller than this threshold, the output active power is forced to zero. This ensures that, under no-load conditions, even with minor noise signals, the active power register output remains 0.

Table 15 anti-creep threshold register

| Addr | Name     | Bit Width | Default Value | Description                       |

|------|----------|-----------|---------------|-----------------------------------|

| 88   | WA_CREEP | 12        | 0x04C         | Active Power Anti-Creep Threshold |

When the chip is in anti-creep mode, power values below the threshold are excluded from energy accumulation.

#### 7.1.2.6 Small-Signal Compensation for Active Power

For active power calculation, the small-signal compensation register can be used to adjust nonlinear errors in the small-signal range, thereby reducing noise-induced errors.

The active power small-signal compensation register (WA\_LOS) is a 12-bit two's complement value with a default setting of 0x000.

Table 16 small-signal compensation registers

| Addr | Name     | Bit Width | Default Value | Description                                                           |

|------|----------|-----------|---------------|-----------------------------------------------------------------------|

| 84   | A_WA_LOS | 12        | 0x000         | Channel A Active Power Small-Signal Compensation,<br>Two's Complement |

| 85   | B_WA_LOS | 12        | 0x000         | Channel B Active Power Small-Signal Compensation,<br>Two's Complement |

#### 7.1.3 Active Energy Measurement Principle

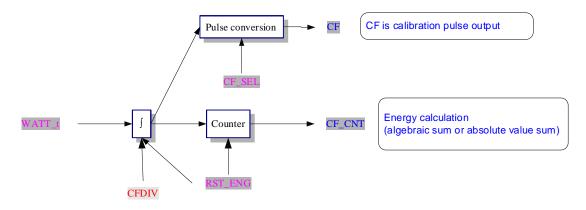

Figure 4 Active Energy Signal Chain

By integrating active power over a period of time, the active energy during that period can be obtained. This energy is further converted into corresponding frequency calibration pulses (CF). The more

electricity is consumed, the faster the CF frequency; the less electricity is consumed, the slower the CF frequency.

## 7.1.3.1 Active Energy Output

The energy (electricity consumption) can be obtained by counting CF pulses, which are stored in the energy pulse accumulation register X CF CNT.

Table 17 Active Energy Pulse Counters

| Addr | Name     | Bit Width | Default Value | Description                                      |

|------|----------|-----------|---------------|--------------------------------------------------|

| 26   | A_CF_CNT | 24        | 0x000000      | Channel A Active Energy Pulse Counter (Unsigned) |

| 27   | B_CF_CNT | 24        | 0x000000      | Channel B Active Energy Pulse Counter (Unsigned) |

The active energy register is used to store the continuously accumulated active energy.

Table 18 Accumulated Active Energy Registers

| Addr | Name     | Bit Width | Default Value | Description                                     |

|------|----------|-----------|---------------|-------------------------------------------------|

| 1C   | A_WATTHR | 24        | 0x000000      | Channel A Active Energy Accumulation (Unsigned) |

| 1D   | B_WATTHR | 24        | 0x000000      | Channel B Active Energy Accumulation (Unsigned) |

## 7.1.3.2 Active Energy Output Selection

The CF pulse output representing energy information can be configured via MODE\_OUT.

Table 19 CF Output Channel Selection

| 0x43  | MODE_OUT       | Operation Mode Register   |                                    |  |

|-------|----------------|---------------------------|------------------------------------|--|

| No.   | name           | default value description |                                    |  |

|       |                |                           | CF Output Channel Selection:       |  |

|       |                |                           | 0000-Default (CF output disabled); |  |

|       |                |                           | 0001-A_CF; 0010-B_CF;              |  |

| [7:4] | CF_SEL 4'b0000 | 4'b0000                   | 0011-A_CFQ; 0100-B_CFQ;            |  |

|       |                |                           | 0101-A_CF_DC; 0110-B_CF_DC;        |  |

|       |                |                           | 0111-A_CFS; 1000-B_CFS;            |  |

|       |                |                           | 1001-A_CF_SUM; 1010-B_CF_SUM;      |  |

MODE[11] (CF\_ADD\_SEL) can be used to set the energy accumulation method: algebraic sum or absolute value sum.

The counting results of CF pulses are stored in the corresponding pulse counting registers. The CF pin can also be configured to output meter calibration pulses. When the CF pulse period is less than 180ms, it outputs a 50% duty cycle pulse. When the period is greater than or equal to 180ms, the high-level duration is fixed at 90ms.

#### 7.1.3.3 Active Energy Output Scaling

During energy accumulation, the accumulation rate can be adjusted through the CF\_DIV register with 12 gear settings, each having a 2x relationship (coarse adjustment).

Table 20 CF Scaling Factor Register

| Addr | Name  | Bit Width | Default Value | Description                |

|------|-------|-----------|---------------|----------------------------|

| A2   | CFDIV | 12        | 0x010         | CF Scaling Factor Register |

Taking the default value 0x010 as the reference pulse output, the output pulse frequency ratios relative to CFDIV=0x010 for other settings are as follows.

Table 21 CF Scaling Factor

| CFDIV | Scaling Factor | CFDIV | Scaling Factor |

|-------|----------------|-------|----------------|

| 0x000 | 0.03125        | 0x040 | 4              |

| 0x001 | 0.0625         | 0x080 | 8              |

| 0x002 | 0.125          | 0x100 | 16             |

| 0x004 | 0.25           | 0x200 | 32             |

| 0x008 | 0.5            | 0x400 | 64             |

| 0x010 | 1              | 0x800 | 256            |

| 0x020 | 2              |       |                |

The relationship between pulse period and CFDIV/WATT register values is given by the formula:

$$t_{CF} = \frac{4194304 \times 0.032768 \times 32}{CFDIV \times WATT}$$

#### 7.1.4 Current and Voltage RMS Calculation Principle

The RMS calculation principle for channels is illustrated in the figure below.

Figure 5 RMS calculation Signal Chain

The original waveform of the channel is processed through a squaring circuit (X²), an RMS low-pass filter (LPF\_RMS), and a square root circuit (ROOT) to obtain the instantaneous RMS value (RMS\_t). This value is then averaged to derive the mean RMS values for current (I\_RMS) and voltage (V\_RMS).

#### 7.1.4.1 RMS Output

The RMS calculation results are stored in the RMS register, which is a 24-bit unsigned value.

Table 22 RMS Register

| Addr | Name   | Bit Width | Default Value | Description                               |

|------|--------|-----------|---------------|-------------------------------------------|

| 7    | IA_RMS | 24        | 0x000000      | Current Channel A RMS Register (Unsigned) |

| 8    | IB_RMS | 24        | 0x000000      | Current Channel B RMS Register (Unsigned) |

| 9    | V_RMS  | 24        | 0x000000      | Voltage Channel RMS Register (Unsigned)   |

When a channel enters the anti-creep state for RMS measurement, the value of its RMS register is forced to zero and stops updating.

# 7.1.4.2 RMS Input Signal Configuration

The waveform for RMS calculation can be configured as Full-wave, AC full-wave, or DC. The full-wave waveform is output without passing through the HPF. In AC measurement mode (with HPF enabled), the AC full-wave waveform is output. In DC measurement mode (with LPF enabled for DC extraction), the DC waveform is output. These modes can be configured via the user-mode register MODE.

Table 23 RMS waveform selection

| 0x44  | MODE         | Operation Mode Register   |                                                                                                                                   |  |

|-------|--------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|

| No.   | name         | default value description |                                                                                                                                   |  |

| [9:4] | WAVE_RMS_SEL | 2'b00                     | RMS waveform selection: 00-HPF, 10-DC, 01-SINC, 11-HPF [9:8]: Voltage channel; [7:6]: Current B channel; [5:4]: Current A channel |  |

#### 7.1.4.3 RMS Refresh Rate Setting

By configuring the RMS\_UPDATE\_SEL bits in MODE[14:13], the average refresh time for RMS values can be selected.

Table 24 RMS register update rate selection

| 0x44    | MODE           | Operation Mode Register |                                                                                        |

|---------|----------------|-------------------------|----------------------------------------------------------------------------------------|

| No.     | name           | default value           | description                                                                            |

| [14:13] | RMS_UPDATE_SEL | 2'b00                   | RMS register update rate selection, 11-1000ms, 00-500ms (default), 01-250ms, 10- 125ms |

#### 7.1.4.4 Current/Voltage RMS Calibration

Two 24-bit RMS offset correction registers (RMSOS) with a default value of 0x000000 (two's complement). Two 16-bit RMS gain correction registers (RMSGN) with a default value of 0x0000 (two's complement).

These registers are used to calibrate deviations in RMS calculations. Such deviations may originate from input noise, as the RMS calculation involves a squaring operation that could introduce DC offsets caused by noise. Gain and offset corrections ensure the RMS register values approach 0 under no-load conditions.

Table 25 RMS adjustment

| Addr | Name     | Bit Width | Default Value | Description                                               |

|------|----------|-----------|---------------|-----------------------------------------------------------|

| 6C   | IA_RMSOS | 16        | 0x0000        | Current channel A RMS offset adjustment, two's complement |

| 6D   | IB_RMSOS | 16        | 0x0000        | Current channel B RMS offset adjustment, two's complement |

| 6E   | V_RMSOS  | 16        | 0x0000        | Voltage channel RMS offset adjustment, two's complement   |

| 71   | IA_RMSGN | 16        | 0x0000        | Current channel A RMS gain adjustment, two's              |

|    |          |    |        | complement                                              |

|----|----------|----|--------|---------------------------------------------------------|

| 72 | IB_RMSGN | 16 | 0x0000 | Current channel B RMS gain adjustment, two's complement |

| 73 | V_RMSGN  | 16 | 0x0000 | Voltage channel RMS gain adjustment, two's complement   |

RMS Offset Calibration Formula:

$$RMS = \sqrt{RM{S_0}^2 + RMSOS \times 1024}$$

RMS Gain Calibration Formula:

$$RMS = RMS0 * (1 + \frac{RMSGN}{2^{16}})$$

where RMS0 represents the RMS value before channel calibration, and RMS is the RMS value after channel calibration.

The adjustment range of RMSGN is ±50%.

#### 7.1.4.5 RMS Anti-Creep Function

Equipped with patented RMS anti-creep technology to ensure zero RMS output when no current is input. The RMS anti-creep threshold register (RMS\_CREEP) is a 12-bit unsigned value, defaulting to 0x200.

This value is multiplied by 2 and compared with the absolute value of the input RMS signal. If the input RMS signal is smaller than this threshold, the output RMS is forced to zero. This ensures that, under no-load conditions, even in the presence of minor noise signals, the value written to the RMS register remains zero.

Table 26 RMS Small Signal Threshold Register

| Addr | Name      | Bit Width | Default Value | Description                         |

|------|-----------|-----------|---------------|-------------------------------------|

| 8A   | RMS_CREEP | 12        | 0x200         | RMS Small Signal Threshold Register |

#### 7.1.5 Principle of Fast RMS Detection

The principle of fast RMS calculation is illustrated in the figure below.

Figure 6 Fast RMS calculation Signal Chain

The current channel features a fast RMS register capable of detecting half-cycle or full-cycle RMS values. This function can be used for leakage current or overcurrent detection.

The input waveform undergoes absolute value processing, followed by integration over a specified time period to obtain the fast RMS value. This value I\_FAST\_RMS[23:3] is compared with a preset threshold FAST\_RMS\_CTRL[20:0]. If exceeded, a flag can be triggered.

# 7.1.5.1 Fast RMS Output

The fast RMS output registers for current and voltage channels are as follows. These registers are 24-bit unsigned values.

Table 27 Fast RMS Register

| Addr | Name        | Bit<br>Width | Default<br>Value | Description                         |

|------|-------------|--------------|------------------|-------------------------------------|

| Α    | IA_FAST_RMS | 24           | 0x000000         | Current Channel A Fast RMS Register |

| В    | IB_FAST_RMS | 24           | 0x000000         | Current Channel B Fast RMS Register |

| С    | V_FAST_RMS  | 24           | 0x000000         | Voltage Channel Fast RMS Register   |

## 7.1.5.2 Fast RMS Input Selection

The waveforms for fast RMS calculation include full-wave and AC full-wave. The full-wave waveform is output without passing through the HPF.

When using the HPF, it operates in AC measurement mode, outputting the AC full-wave waveform. This can be configured via the user mode register MODE[0].

Table 28 Fast measurement selection

| 0x96 | MODE1   | Operation Mode Register |                                                                                                 |  |  |

|------|---------|-------------------------|-------------------------------------------------------------------------------------------------|--|--|

| No.  | name    | default value           | efault value description                                                                        |  |  |

| [0]  | L_F_SEL | 1'b0                    | Fast measurement selection via HPF. Default 0-No HPF (full wave), 1-HPF selected (AC full wave) |  |  |

#### 7.1.5.3 Fast RMS Accumulation Time and Threshold

For fast RMS calculation, the absolute value is first taken, followed by integration based on the preset accumulation time. Typically, integer multiples of half-cycle or full-cycle durations are selected.

Table 29 Fast RMS Accumulation Time and Threshold

| Addr | Name              | Bit<br>Width | Default<br>Value | Description                                                                                                                                                                                        |

|------|-------------------|--------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 94   | IA_FAST_RMS_CTRL1 | 12           | 0x20F            | [11:9] Refresh time for the channel's fast RMS register. Options include half-cycle or N full cycles. The default is one full cycle; [8:0] Upper bits [20:12] of the channel's fast RMS threshold. |

| 95   | IA_FAST_RMS_CTRL2 | 12           | 0xFFF            | Lower bits [11:0] of the channel's fast RMS threshold.                                                                                                                                             |

| 96   | IB_FAST_RMS_CTRL1 | 12           | 0x20F            | [11:9] Refresh time for the channel's fast RMS register. Options include half-cycle or N full cycles. The default is one full cycle; [8:0] Upper bits [20:12] of the channel's fast RMS threshold. |

| 95   | IB_FAST_RMS_CTRL2 | 12           | 0xFFF            | Lower bits [11:0] of the channel's fast RMS threshold.                                                                                                                                             |

| 97   | V_FAST_RMS_CTRL1  | 12           | 0x20F            | [11:9] Refresh time for the channel's fast RMS register. Options include half-cycle or N full cycles. The default is one full cycle; [8:0] Upper bits [20:12]                                      |

|    |                  |    |       | of the channel's fast RMS threshold.                   |

|----|------------------|----|-------|--------------------------------------------------------|

| 95 | V_FAST_RMS_CTRL2 | 12 | 0xFFF | Lower bits [11:0] of the channel's fast RMS threshold. |

The accumulation time is configured via FAST\_RMS\_CTRL1[11:9], with six options: 000 - 10ms, 001 - 20ms, 010 - 40ms, 011 - 80ms, 100 - 160ms, 101 - 320ms. By default, the full-cycle accumulation response time of 20ms is selected. A longer accumulation time results in smaller fluctuations.

FAST\_RMS\_CTRL1[8:0] | FAST\_RMS\_CTRL2[11:0] is used to set the fast RMS over-limit threshold. Once the fast RMS register value [23:3] exceeds this threshold, the output flag (flag) is set to 1. This flag is connected to the output (MF) and can directly pull the overcurrent indication pin high. It can be used in conjunction with the overcurrent indication control register.

## 7.1.5.4 Power Grid Frequency Selection

The AC FREQ SEL register allows selection between 50Hz and 60Hz power grid applications.

| 0x44 | MODE        | Operating Mode Register |                              |  |

|------|-------------|-------------------------|------------------------------|--|

| No.  | name        | default value           | description                  |  |

|      |             |                         | AC frequency selection:      |  |

| [15] | AC_FREQ_SEL | 1'b0                    | 1 = 60 Hz                    |  |

|      |             |                         | 0 = 50 Hz (default is 50 Hz) |  |

Table 30 AC frequency selection

# 7.1.5.5 Fast RMS Overlimit Data Storage

To record fast overload signals, the fast RMS overlimit feature includes data retention functionality. Specific register operations are required to clear the related FAST\_RMS\_HOLD registers. Refer to the following table for details:

| Addr | Name             | Bit Width | Default Value | Description                                         |

|------|------------------|-----------|---------------|-----------------------------------------------------|

| 39   | IA_FAST_RMS_HOLD | 24        | 0x000000      | Current Channel A Fast RMS Register, unsigned, hold |

| 3A   | IB_FAST_RMS_HOLD | 24        | 0x000000      | Current Channel B Fast RMS Register, unsigned, hold |

| 3B   | IA_FAST_RMS_HOLD | 24        | 0x000000      | Voltage Channel Fast RMS Register, unsigned, hold   |

Table 31 Fast RMS Register

#### 7.1.5.6 Overcurrent Indication

The overcurrent indication (MF) can be controlled through the following overcurrent indication control registers:

Table 32 Overcurrent indication control register

| Addr | Name       | Bit Width | Default Value | Description                               |

|------|------------|-----------|---------------|-------------------------------------------|

| 9B   | flag_ctrl1 | 16        | 0x0000        | Overcurrent indication control register 1 |

| 9C   | flag_ctrl2 | 16        | 0x0000        | Overcurrent indication control register 2 |

## 7.1.5.7 Relay Control

The output level of the MF pin can also be directly controlled by writing to the flag\_ctrl register to control relays:

Table 33 Relay Control

| Addr | Name      | Bit Width | Default Value              | Description                                                |

|------|-----------|-----------|----------------------------|------------------------------------------------------------|

|      |           |           |                            | [11:9]: Master control selection for MF3–MF1:              |

|      |           |           |                            | 0 = output internal indicator;                             |

|      |           |           |                            | 1 = directly controlled by master                          |

|      |           |           |                            | [8:6]: Output level of MF3–MF1 when directly controlled by |

|      |           |           |                            | master                                                     |

| 9A   | flag_ctrl | 12        | 0x000                      | [5:3]: Indicator selection for MF3–MF1:                    |

|      |           |           |                            | 0 = output real-time interrupt;                            |

|      |           |           | 1 = output delayed control |                                                            |

|      |           |           |                            | [2:0]: Delay control for MF3–MF1=0:                        |

|      |           |           |                            | 0 = Disable,                                               |

|      |           |           |                            | 1 = Enable                                                 |

#### 7.1.6 Electrical Parameter Measurement

## 7.1.6.1 Line Frequency Measurement

The grid frequency is measured through the voltage channel.

The count value recorded in the PERIOD register corresponds to the line voltage cycle period. If the input signal deviates from 50Hz/60Hz, the corresponding count value will change.

Table 34 Line voltage frequency/period register

| Addr | Name   | Bit<br>Width | Default Value | Description                            |

|------|--------|--------------|---------------|----------------------------------------|

| 35   | PERIOD | 20           | 0x000000      | Line voltage frequency/period register |

#### 7.1.6.2 Phase Angle Calculation

The principle of phase angle measurement is illustrated in the figure below.

Figure 7 phase angle measurement

The phase difference is obtained by calculating the time interval between the positive zero-crossings of current and voltage. The corresponding time value is updated to the ANGLE register, which is a 16-bit unsigned number.

Table 35 AC frequency selection

| Addr | Name     | Bit<br>Width | Default Value | Description                                                  |

|------|----------|--------------|---------------|--------------------------------------------------------------|

| 36   | A_CORNER | 16           | 0x0000        | Phase angle register between current A and voltage waveforms |

| 37   | B_CORNER | 16           | 0x0000        | Phase angle register between current B and voltage waveforms |

### 7.1.6.3 Power Sign Bit

For the power pulse CF output, there is a sign bit register that indicates the direction of CF. This direction signifies whether the corresponding accumulated energy during the period from the previous CF pulse to the current CF pulse is in the power consumption or power generation direction.

Table 36 Power Sign Bit Register

| Addr | Name | Bit Width | Default Value | It Value Description                                                                           |  |

|------|------|-----------|---------------|------------------------------------------------------------------------------------------------|--|

| 30   | SIGN | 10        | 0x000         | Sign bit corresponding to the current energy pulse count, refreshed upon each CF pulse output. |  |

#### 7.1.7 Fault Detection

## 7.1.7.1 Zero-Crossing Detection

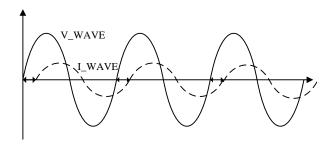

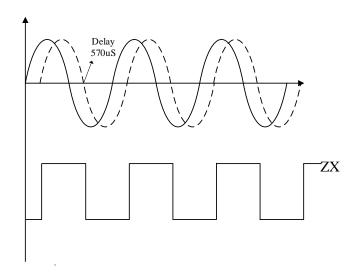

Voltage zero-crossing detection is provided. When zx is 0, it indicates the positive half-cycle of the waveform; when zx is 1, it indicates the negative half-cycle. The output is a fundamental zero-crossing signal that has passed through a HPF filter, introducing a delay of approximately 570us compared to the actual input signal.

The zero-crossing signal is primarily used to assist in disconnecting the relay at the zero-crossing point, which helps reduce relay sticking.

Figure 8 Zero-Crossing Detection

Note: To prevent uncertainties caused by stray signals from background noise or small signals, the current zero-crossing threshold is set to 70,000, and the voltage zero-crossing threshold is 200,000. If the instantaneous RMS value is smaller than the threshold, the ZX signal will be uncertain.

The zero-crossing signal output is configured as /ZX (ZX inverted) via the /IRQ pin.

#### 7.1.7.2 Peak Overlimit

Threshold values for current and voltage RMS can be set via peak threshold registers (I\_PKLVL, V PKLVL).

Addr Name Bit Width **Default Value Description** [15:12]: Number of consecutive half-cycles for detection 8C  $V_PKLVL$ 16 0xFFFF [11:0]: Voltage peak threshold register V\_PKLVL [15:12]: Number of consecutive half-cycles for detection 8D I\_PKLVL 16 0xFFFF [11:0]: Current peak threshold register I\_PKLVL

Table 37 peak threshold register

For example: when the current fast RMS exceeds the threshold set in the current peak threshold register (I\_PKLVL), a current overload indication PKI is triggered. If the corresponding PKI enable bit in the interrupt mask register (MASK) is set to logic 0, the /IRQ logic output becomes active low.

Similarly, when the voltage fast RMS exceeds the threshold set in the voltage peak threshold register (V\_PKLVL), a voltage overload indication PKV is triggered. If the corresponding PKV enable bit in the interrupt mask register (MASK) is set to logic 0, the /IRQ logic output becomes active low.

| 0x3F     | STATUS         |               |                                         |

|----------|----------------|---------------|-----------------------------------------|

| Position | Interrupt Flag | Default Value | Description                             |

| 5        | PK_IA          | 0             | Current Channel A peak overlimit signal |

| 6        | PK_IB          | 0             | Current Channel B peak overlimit signal |

| 7        | PK_V           | 0             | Voltage channel peak overlimit signal   |

Table 38 peak overlimit signal

## 7.1.7.3 Line Voltage Sag

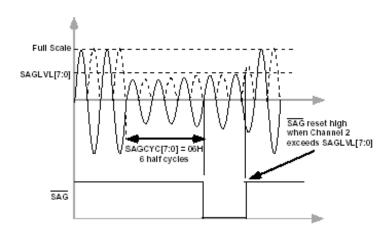

A line voltage sag indication is triggered when the RMS value of the line voltage remains below a certain threshold for more than a specified number of half cycles.

Figure 9 Sag Detection

As shown in the figure above, when the voltage RMS falls below the threshold set in the sag voltage threshold register (SAGLVL) and the duration exceeds the time configured in the sag line cycle register

(SAGCYC) (illustrated as exceeding the 6th half cycle, where SAGCYC[11:0] = 06H), the line voltage sag event is recorded by setting the SAG flag in the interrupt status register (STATUS).

Table 39 Line voltage sag register

| 0x3F     | STATUS         |               |                           |

|----------|----------------|---------------|---------------------------|

| Position | Interrupt Flag | Default Value | Description               |

| 3        | SAG            | 0             | Line voltage sag detected |

If the corresponding SAG enable bit in the interrupt mask register (MASK) is set to logic 0, the /IRQ output becomes active low.

The sag cycle count and sag voltage threshold can be configured. The sag voltage threshold register (SAGLVL) allows user read/write access with a default value of 0x100, while the sag line cycle register (SAGCYC) also supports user read/write operations with a default value of 0x04.

Table 40 Sag cycle count and Sag voltage threshold register

| Addr | Name   | Bit<br>Width | Default Value | Description                                                                                                                                                                                                                               |

|------|--------|--------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 91   | SAGCYC | 8            | 0x04          | Sag cycle count (SAGCYC)                                                                                                                                                                                                                  |

| 92   | SAGLVL | 12           | 0x100         | Sag voltage threshold register (SAGLVL). If the voltage channel input remains continuously below this threshold for longer than the duration specified in SAGCYC, a line voltage sag interrupt will be triggered. Default value is 0x100. |

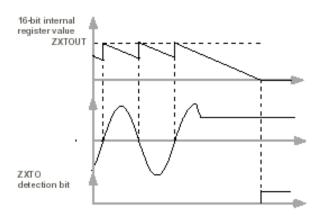

#### 7.1.7.4 Zero-Crossing Timeout

The zero-crossing detection circuit is connected to a timeout detection register ZXTOUT. Each time a zero-crossing signal is detected on the voltage channel, ZXTOUT is reset to its initial value. If no zero-crossing signal is detected, the register value decrements. If no zero-crossing signal is output for an extended period, the register value will reach 0, at which point the corresponding ZXTO bit in the interrupt status register is set to 1. If the corresponding enable bit ZXTO in the interrupt mask register is set to 0, the zero-crossing timeout event will also be reflected on the interrupt pin /IRQ. Regardless of the setting of the corresponding enable bit in the interrupt register, the ZXTO flag in the interrupt status register (MASK) is always set to active 1 when the ZXTOUT register decrements to 0.

Table 40 ZXTO

| 0x3F     | STATUS         |               |                       |

|----------|----------------|---------------|-----------------------|

| Position | Interrupt Flag | Default Value | Description           |

| 4        | ZXTO           | 0             | zero-crossing timeout |

#### Table 40 ZXTOUT

| Addr | Name   | Bit Width | Default Value | Description                                                                                                                                                         |

|------|--------|-----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8E   | ZXTOUT | 16        | 0xFFFF        | If no zero-crossing signal is detected within the duration specified by this register, a zero-crossing timeout interrupt will be generated. Default value is FFFFH. |

The zero-crossing timeout register ZXTOUT supports both read and write operations by users, with a default value of 0xFFFF. The register has a resolution of 64µs/LSB, thereby limiting the maximum interrupt delay time to 4.26 seconds.

The following diagram illustrates the zero-crossing timeout detection mechanism when the line voltage remains at a fixed DC signal level:

Figure 10 Zero-Crossing Timeout

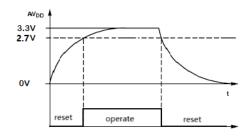

#### 7.1.7.5 Power Supply Monitoring

The chip integrates an on-board power monitoring circuit that continuously monitors the analog supply voltage (VDD). If the supply voltage falls below  $2.7V \pm 5\%$ , the entire circuit remains deactivated (non-operational), meaning no energy accumulation is performed when VDD < 2.7V. This design ensures correct operation during power-up/power-down events.

The power monitoring circuit incorporates hysteresis and filtering mechanisms to significantly suppress false triggering caused by noise. Under normal conditions, the power supply decoupling network should maintain VDD ripple within  $3.3V \pm 5\%$ .

Figure 11 Power Supply Monitoring

#### 7.2. Internal Registers

#### 7.2.1 Electrical Parameter Registers (Read-Only)

## Table 44 Electrical Parameter Registers

|      | Table 14 Electroal Farameter Registers |              |                  |                                                 |  |  |  |

|------|----------------------------------------|--------------|------------------|-------------------------------------------------|--|--|--|

| Addr | Name                                   | Bit<br>Width | Default<br>Value | Description                                     |  |  |  |

| 1    | IA_WAVE                                | 24           | 0x000000         | Current A waveform                              |  |  |  |

| 2    | IB_WAVE                                | 24           | 0x000000         | Current B waveform                              |  |  |  |

| 3    | V_WAVE                                 | 24           | 0x000000         | Voltage waveform                                |  |  |  |

| 4    | IA_WAVE_DC                             | 24           | 0x000000         | Current A DC waveform                           |  |  |  |

| 5    | IB_WAVE_DC                             | 24           | 0x000000         | Current B DC waveform                           |  |  |  |

| 6    | V_WAVE_DC                              | 24           | 0x000000         | Voltage DC waveform                             |  |  |  |

| 7    | IA_RMS                                 | 24           | 0x000000         | RMS of Current A                                |  |  |  |

| 8    | IB_RMS                                 | 24           | 0x000000         | RMS of Current B                                |  |  |  |

| 9    | V_RMS                                  | 24           | 0x000000         | RMS of Voltage                                  |  |  |  |

| A    | IA_FAST_RMS                            | 24           | 0x000000         | Fast RMS of Current A                           |  |  |  |

| В    | IB_FAST_RMS                            | 24           | 0x000000         | Fast RMS of Current B                           |  |  |  |

| С    | V_FAST_RMS                             | 24           | 0x000000         | Fast RMS of Voltage                             |  |  |  |

| 10   | A_WATT                                 | 24           | 0x000000         | Active power (channel A), signed                |  |  |  |

| 11   | B_WATT                                 | 24           | 0x000000         | Active power (channel B), signed                |  |  |  |

| 12   | A_VAR                                  | 24           | 0x000000         | Reactive power (fundamental, A), signed         |  |  |  |

| 13   | B_VAR                                  | 24           | 0x000000         | Reactive power (fundamental, B), signed         |  |  |  |

| 14   | A_WATT_DC                              | 24           | 0x000000         | DC power (channel A)                            |  |  |  |

| 15   | B_WATT_DC                              | 24           | 0x000000         | DC power (channel B)                            |  |  |  |

| 16   | A_VA                                   | 24           | 0x000000         | Apparent power (channel A)                      |  |  |  |

| 17   | B_VA                                   | 24           | 0x000000         | Apparent power (channel B)                      |  |  |  |

| 18   | A_WATT_SUM                             | 24           | 0x000000         | Total active power (AC + DC, channel A), signed |  |  |  |

|      | •                                      | •            |                  |                                                 |  |  |  |

# **BL0973**

| 19         B_WATT_SUM         24         0x000000         Total active power (AC + DC, channel B), signed           1A         A_PF         24         0x000000         Power factor (channel A), signed           1B         B_PF         24         0x000000         Power factor (channel B), signed           1C         A_WATHR         24         0x000000         Active energy (channel A)           1D         B_WATTHR         24         0x000000         Reactive energy (fundamental, A)           1E         A_VARHR         24         0x000000         Reactive energy (fundamental, B)           20         A_DCHR         24         0x000000         DC energy (channel B)           21         B_DCHR         24         0x000000         DC energy (channel B)           22         A_VAHR         24         0x000000         Apparent energy (channel B)           23         B_VAHR         24         0x000000         Apparent energy (channel B), unsigned (optional)           24         A_SUMHR         24         0x000000         Total active energy (channel B)           25         B_SUMHR         24         0x000000         Total active energy (channel B)           26         A_CF_CNT         24         0x000000         Active pulse count (ch                   |    |              |    |          |                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--------------|----|----------|--------------------------------------------------|

| 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 | B_WATT_SUM   | 24 | 0x000000 | Total active power (AC + DC, channel B), signed  |

| 1C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1A | A_PF         | 24 | 0x000000 | Power factor (channel A), signed                 |

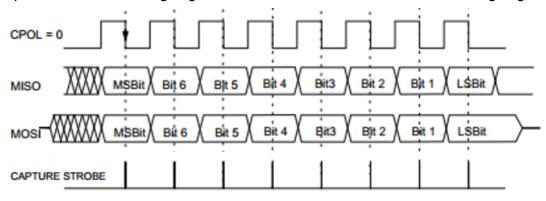

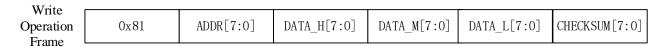

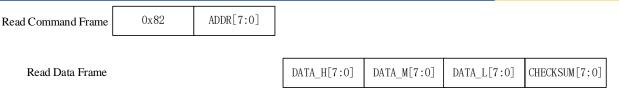

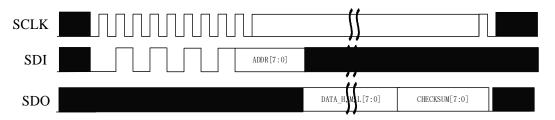

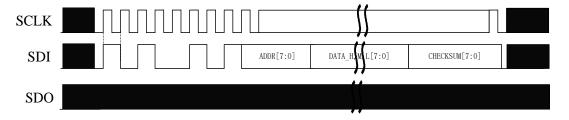

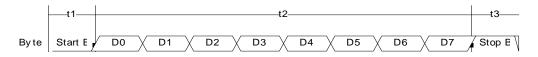

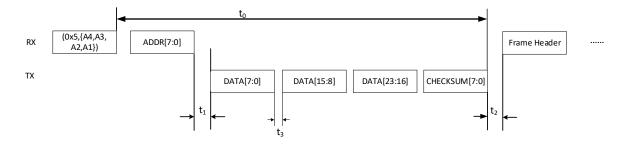

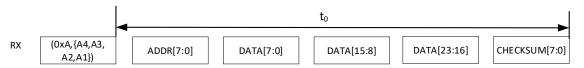

| D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1B | B_PF         | 24 | 0x000000 | Power factor (channel B), signed                 |