## 40V, 600mA step-down voltage stabilizing circuit

## Description

BL9342 is a high frequency (1.8MHz) step-down switching regulator with integrated high-side highvoltage power MOSFET. Provide a single highefficiency output 0.6A maximum, and achieve fast loop response in current mode control mode.

Wide range of input voltage (4.2V to 40V) can realize various applications of buck power conversion. Low turn-off current is suitable for battery-powered applications.

Under the condition of light load, the loss of switch and gate drive can be reduced by reducing the switching frequency, and the high-efficiency power conversion in a wide load range can be realized.

The frequency folding technology is helpful to prevent the inductor current from getting out of control at startup. Thermal shutdown provides reliable and fault-tolerant operation.

## Applications

- High voltage power conversion

- Instrument

- Industrial power system

- Distributed power system

- Battery powered system

## Features

- 230uA working static current

- Wide operating voltage range from 4.2V to 40V

- 500mΩ internal power MOSFET

- 1.8MHz fixed switching frequency

- Internal compensation

- Ceramic output capacitor voltage stabilization

- Internal soft start

- Precision current limit without sampling resistor

- The maximum efficiency can reach 90%

- Low turn-off current

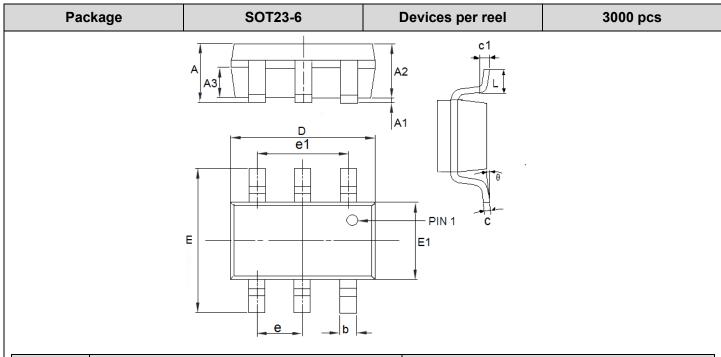

## Package

6-pin SOT23-6

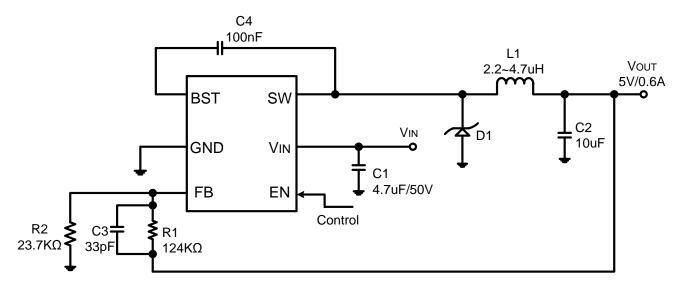

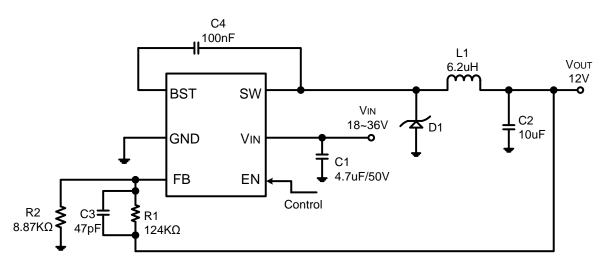

# **Typical Application Circuit**

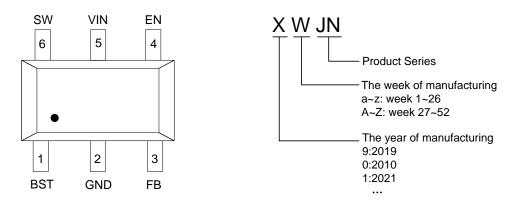

# Pin Configuration and Marking Information

# **Pin Assignment**

| Pin No. | Symbol          | Function                                                                               |

|---------|-----------------|----------------------------------------------------------------------------------------|

| 1       | BST             | Bootstrap pin. The internal floating high-side MOSFET drives the positive power        |

| I       | 001             | source of the tube. Connect a bypass capacitor between this pin and SW.                |

| 2       | GND             | Ground. It is connected as close to output capacitor as possible, avoiding the high    |

|         |                 | current switching path.                                                                |

|         | FB              | Feedback. Input of the error amplifier. An external resistor divider connected to the  |

| 3       |                 | output and ground is compared with the internal reference of +0.794V to set the        |

|         |                 | regulated voltage.                                                                     |

|         | EN              | Enable input. Pulling the pin voltage below the specified threshold will turn off the  |

| 4       |                 | chip. Pull above the specified threshold to make the chip work. Suspended chip off.    |

|         |                 | Connect 100k $\Omega$ resistor to V <sub>IN</sub> to turn on automatically.            |

| 5       | V <sub>IN</sub> | Power input. All internal control circuits supply power, including switch tubes. A     |

|         |                 | decoupling capacitor needs to be connected to ground to reduce switching spikes.       |

| 6       | SW              | Switch pin. This is the high-side switch output. It is necessary to connect a Schottky |

|         |                 | diode with low VF to the ground to reduce switching spikes.                            |

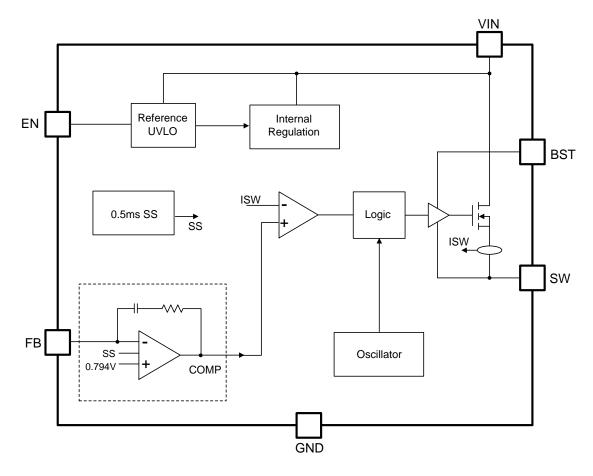

## **Functional Block Diagram**

## **Absolute Maximum Ratings**

| Parameter                               | Range                         | Unit |

|-----------------------------------------|-------------------------------|------|

| Supply voltage (V <sub>IN</sub> )       | -0.3 ~ 43                     | V    |

| Switch voltage (V <sub>Sw</sub> )       | $-0.3 \sim V_{IN(MAX)} + 0.3$ | V    |

| BST to SW voltage                       | -0.3 ~ 6                      | V    |

| Other pins voltage                      | -0.3 ~ 5                      | V    |

| Power dissipation (P <sub>D</sub> )     | 0.63                          | W    |

| Thermal resistance ( $\theta_{JA}$ )    | 200                           | °C/W |

| Maximum junction temperature (TJ)       | 150                           | °C   |

| Storage temperature (T <sub>STG</sub> ) | -65 ~ +150                    | °C   |

| Lead temperature                        | 260                           | C°   |

## Note:

1. Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product.

2. The maximum allowable power dissipation is a function of the maximum junction temperature  $T_{J (MAX)}$ , the junctionto-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_{D(MAX)}=(T_{J(MAX)}-T_A)/\theta_{JA}$ .

3. The  $\theta_{JA}$  values given in this table are for comparison with other packages only and cannot be used for design purposes. They do not represent the performance achieved in real-world applications.

# **Recommended Operate Conditions**

| Parameter                                        | Min | Мах | Unit |

|--------------------------------------------------|-----|-----|------|

| Supply voltage (V <sub>IN</sub> )                | 4.2 | 40  | V    |

| Terminal voltage (VOUT of SW)                    | -   | 40  | V    |

| Operating junction temperature (T <sub>J</sub> ) | -40 | 125 | C°   |

## **Electrical Characteristics**

$V_{\text{IN}}\text{=}12\text{V},\,V_{\text{EN}}\text{=}2\text{V},\,T_{\text{A}}\text{=}25^\circ\text{C},\,\text{unless otherwise specified.}$

| Parameter                      | Symbol                    | Test Condition                           | Min   | Тур.  | Мах   | Unit |

|--------------------------------|---------------------------|------------------------------------------|-------|-------|-------|------|

| Feedback voltage               | V <sub>FB</sub>           |                                          | 0.778 | 0.794 | 0.810 | V    |

| On resistance of switch        | R <sub>sw</sub>           | V <sub>BST</sub> -V <sub>SW</sub> =5V    |       | 500   |       | mΩ   |

| Switching leakage current      | I <sub>SW leak</sub>      | V <sub>EN</sub> =0V, V <sub>SW</sub> =0V |       | 0.1   | 1     | uA   |

| Limiting current               | I <sub>LIM</sub>          |                                          |       | 1     |       | А    |

| Transconductance               | G <sub>CS</sub>           | COMP to SENSE                            |       | 3     |       | A/V  |

| Minimum operating voltage      |                           |                                          | 4.2   |       |       | V    |

| Undervoltage threshold         | V <sub>IN</sub> (UVLO)    |                                          | 3.3   |       | 4.2   | V    |

| Undervoltage return difference | V <sub>IN</sub> (UVLO)HYS |                                          |       | 0.8   |       | V    |

| Soft start time                | T <sub>ss</sub>           | FB from 0 to 1.8V                        |       | 0.5   |       | ms   |

| Oscillating frequency          | Fosc                      |                                          |       | 1.8   |       | MHz  |

| Minimum switch on time         | T <sub>ON MIN</sub>       |                                          |       | 100   |       | ns   |

| Turn off current               | lsd                       | V <sub>EN</sub> <0.3V                    |       | 3     | 15    | uA   |

| Quiescent current              | lsq                       | V <sub>FB</sub> =0.9V, no load           |       | 200   |       | uA   |

| Thermal shutdown               | Temp                      |                                          |       | 150   |       | °C   |

| EN high level                  | V <sub>ENH</sub>          |                                          | 1.6   |       | 2.0   | V    |

| EN return difference           | EN HYS                    |                                          |       | 0.6   |       | V    |

## **Principle of Operation**

BL9342 is a 1.8MHz oscillating frequency, asynchronous step-down switching regulator with integrated high-side high-voltage power MOSFET. Current mode control is adopted to provide a single 0.6A high-efficiency output with internal compensation. It has wide input voltage range, internal soft start control and precise current limit. Very low static working current is suitable for battery-powered application.

### **PWM control**

Under the condition of medium to large output current, the circuit works in the mode of fixed frequency and peak current control to adjust the output voltage. The PWM cycle is generated by the internal clock, and the power MOSFET remains on until its current reaches the set value of COMP voltage. When the power tube is turned off, it will remain off for at least 100ns before the start of the next cycle. In a PWM cycle, if the current in the MOSFET tube does not reach the current value set by COMP, the power MOSFET will remain on, thus saving a switching operation.

### Pulse jump mode

At light load, the circuit enters pulse jump mode to improve light load efficiency. The judgement of pulse jump is based on its internal COMP voltage. If the COMP terminal is lower than the internal sleep threshold, a pause command is generated to prevent the clock pulse from being turned on, so that the power MOSFET cannot be turned on as instructed, which can save driving and switching losses. This pause command will also put the whole chip into sleep mode and consume very low quiescent current to further improve the light load efficiency.

When the COMP voltage is higher than the sleep threshold, the pause signal is reset and the chip returns to normal PWM operation. Every time the pause instruction changes state from low to high, an on signal is immediately generated to turn on the power MOSFET.

## Error amplifier

The error amplifier is composed of an internal operational amplifier and a resistor-capacitor feedback network connected between its output (internal COMP node) and negative input (FB). When FB is lower than its internal reference voltage (REF), COMP is driven higher by the operational amplifier, resulting in higher switching peak current output, so more energy is transferred to the output, and vice versa.

Generally, FB is connected to a voltage divider composed of RUP and RDN, where RDN connects FB and ground, while RUP connects voltage output node and FB. Meanwhile, RUP controls the gain of the error amplifier together with the internal compensation RC network.

#### Internal voltage stabilizing source

Most of the internal circuits are powered by internal 2.6V voltage regulator. The voltage regulator input is  $V_{IN}$  and works in the full  $V_{IN}$  range. When  $V_{IN}$  is greater than 4.0V, the regulator outputs normally. When  $V_{IN}$  is lower than 4.0V, the output also decreases.

#### **Enable control**

The circuit has a special enable control terminal EN. When  $V_{IN}$  is high enough, the chip can be enabled and disabled through the EN terminal. Active high. The lower threshold is 1.6V. Back to 0.6V. When suspended, the EN terminal is pulled to the ground internally, and the chip is disabled. When EN is pulled to 0V, the chip enters the lowest shutdown current mode. When EN is higher than zero but lower than its threshold, the chip is still in shutdown mode but the shutdown current increases slightly.

#### Undervoltage lockout (UVLO)

Undervoltage lockout (UVLO) of input voltage protects the chip from working under the condition of insufficient power supply voltage.

#### Internal soft start

Soft start is adopted to prevent the output voltage of the converter from overshooting at startup. When the chip is started, the internal circuit generates a soft start voltage (SS) which starts from 0V and is set by the soft start time and has a slow rising speed. When it is lower than the internal reference REF, SS is the main reference, and the error amplifier uses SS instead of REF as the reference. When SS is higher than REF, REF is dominant. SS is also associated with FB. SS can be much lower than FB, but only slightly higher than FB. If FB falls unexpectedly, SS will also track FB's decline. This function is designed to deal with short circuit recovery. When the short circuit is eliminated, the SS ramp-up is just like a restart soft start process, which prevents the output voltage from overshooting.

#### Thermal shutdown

Thermal shutdown is to prevent the chip from overheating. When the chip temperature is higher than its upper threshold, the whole chip will be shut down. When the temperature is lower than the lower threshold, the thermal shutdown is eliminated and the chip is re-enabled.

#### Floating driver and bootstrap charging

The floating MOSFET driver of the is powered by an external bootstrap capacitor. The floating drive has its own UVLO protection. The turn-on threshold of the UVLO is about 2.9V, and the return difference is about 300mV. During UVLO, SS voltage is reset to zero. When the UVLO is removed, the controller starts the soft start process.

The bootstrap capacitor is charged by the internal bootstrap voltage regulator and kept at about 5V. When the

voltage between BST and SW is lower than the regulated value, a PMOS switch tube connecting  $V_{IN}$  to BST is turned on, and the charging current is from  $V_{IN}$ , BST and then to SW. The external circuit should provide sufficient voltage margin to facilitate charging.

As long as  $V_{IN}$  is higher than SW, the bootstrap capacitor can be charged. When the power MOSFET is turned on,  $V_{IN}$  is approximately equal to SW, so the bootstrap capacitor cannot be charged. When the external freewheeling diode is turned on, the difference between  $V_{IN}$  and SW is the largest, which is the best period for charging. When there is no current in the inductor, SW is equal to the output voltage  $V_{OUT}$ , and the voltage between  $V_{IN}$  and  $V_{OUT}$  can be used to charge the bootstrap capacitor. Under the working condition of higher duty cycle, the charging time of bootstrap capacitor is shortened, and the bootstrap capacitor may not be charged effectively.

When the external circuit does not have enough voltage and time to charge the bootstrap capacitor, the extra external circuit can be used to ensure the bootstrap voltage within the normal working range.

The UVLO of the suspension driver is not transmitted to the controller.

The DC quiescent current of the floating driver is about 20uA. Ensure that the supply current at SW terminal is higher than this number.

#### **Current comparator and current limit**

Power MOSFET current is accurately sampled by a current sampling MOSFET. And then sent to a high-speed current comparator for current mode control. This sampled current is used as one of the inputs of the current comparator. When the power MOSFET is turned on, the comparator is blanked and then turned on to avoid noise. Then, the comparator compares the power switch current with the COMP voltage, and when the sampling current is higher than the COMP voltage, comparator output is low, turn off power MOSFET. The maximum current of internal power MOSFET is limited by internal cycle by cycle.

#### Startup and shutdown

When V<sub>IN</sub> and EN are higher than their corresponding thresholds, the chip starts to work. The reference power supply is started first to generate stable reference voltage and current. Then the internal voltage stabilizing source is started, which provides stable voltage for other circuits. When the internal voltage reaches the upper rail, an internal timer keeps the power MOSFET off for 50us to prevent power-on fluctuation. The internal soft start part starts to work, which keeps SS output low to ensure that other circuits are ready, and then increases slowly.

Three conditions will shut down the chip: EN low,  $V_{IN}$  low and thermal shutdown. In the shutdown sequence, the signal path is blocked first to avoid any fault triggering. Then the COMP voltage and the internal power supply voltage drop. The floating drive is not subject to this shutdown command, but its charging path is disabled.

## **Application Information**

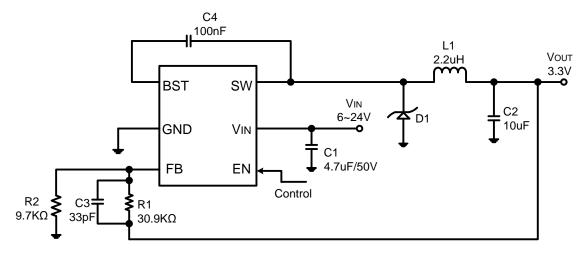

### Set output voltage

The output voltage is set by the voltage divider of the output voltage connected to FB terminal, and the feedback voltage division ratio is as follows:

$$V_{FB} = \frac{R2}{R1 + R2} \times V_{OUT}$$

The feedback resistor R1 also sets the bandwidth of the feedback loop together with the internal compensation capacitor, and R1 is about  $124K\Omega$  to get the best transmission response.

#### Inductance

When the switching voltage is input, the inductor is used to provide continuous current for the output load, and a large inductor can obtain lower output ripple. However, the volume will be larger, the series resistance will be larger and the saturation current will be lower.

Generally, the inductor is selected such that the peak-to-peak value of current in the inductor is 30% of the maximum load current. At the same time, the peak current is less than the maximum switching current, and it will not be saturated under the maximum inductance peak.

#### Input capacitance

The input capacitor (C1) can be electrolytic, tantalum or ceramic capacitor. When electrolytic or tantalum capacitors are used, a small ceramic capacitor, for example, 0.1uF, should be placed near the circuit. When using ceramic capacitors, make sure they have enough capacitance to prevent excessive voltage ripple.

## **Output capacitance**

Output capacitor (C2) is used to hold the output DC voltage. Electrolytic capacitors with low ESR are recommended to keep the output voltage ripple low. The characteristics of the output capacitor will affect the stability of the voltage stabilizing system.

## **Compensating element**

The design goal is to draw up the transfer function of the converter to get an ideal loop gain. And fast transient response and good stability are achieved.

## **Typical application**

3.3V output application diagram

### 12V output application diagram

## **PCB** layout

PCB layout is very important for the stable operation of the circuit. The following suggestions are for reference:

- the switching current path should be as short as possible, and the loop area formed by input capacitor, high-side MOSFET and external switching diode should be as small as possible.

- 2. The bypass ceramic capacitor is placed near the  $V_{IN}$  terminal.

- 3. All feedback circuit connections should be short and direct, and feedback resistors and compensation elements should be as close as possible to the chip.

- 4. SW route is far away from sensitive simulation areas, such as FB.

- 5. SW, IN, and especially ground should be connected to a large copper-clad area to cool the chip, improve thermal performance and enhance long-term reliability.

# Package Information

| DIM | Millimeters |      | Inches      |        |  |

|-----|-------------|------|-------------|--------|--|

|     | Min         | Мах  | Min         | Max    |  |

| А   | 1.05        | 1.45 | 0.0413      | 0.0571 |  |

| A1  | 0           | 0.15 | 0.0000      | 0.0059 |  |

| A2  | 0.9         | 1.3  | 0.0354      | 0.0512 |  |

| A3  | 0.55        | 0.75 | 0.0217      | 0.0295 |  |

| b   | 0.25        | 0.5  | 0.0098      | 0.0197 |  |

| с   | 0.1         | 0.25 | 0.0039      | 0.0098 |  |

| D   | 2.7         | 3.12 | 0.1063      | 0.1228 |  |

| e1  | 1.9(TYP)    |      | 0.0748(TYP) |        |  |

| E   | 2.6         | 3.1  | 0.1024      | 0.1220 |  |

| E1  | 1.4         | 1.8  | 0.0551      | 0.0709 |  |

| е   | 0.95(TYP)   |      | 0.0374(TYP) |        |  |

| L   | 0.25        | 0.6  | 0.0098      | 0.0236 |  |

| θ   | 0           | 8°   | 0.0000      | 8°     |  |

| c1  | 0.2(TYP)    |      | 0.0079(TYP) |        |  |